## HAZARD HANDLING

There are three major types of hazards.

- 1. Data Hazards

- 2. Control Hazards

- 3. Structure Hazards

In our five-stage pipeline design, there are no structure hazards because we have implemented in order execution architecture. So, there is no resource sharing happening in our pipeline.

## Data Hazard Handling

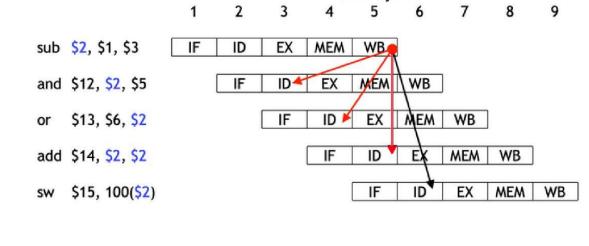

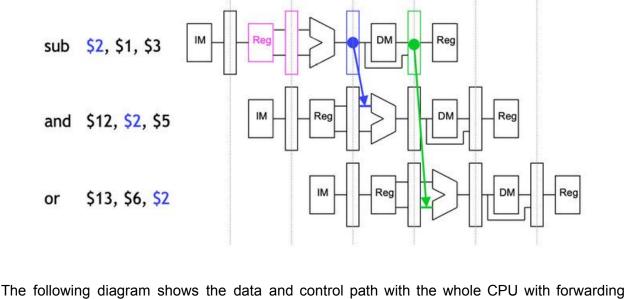

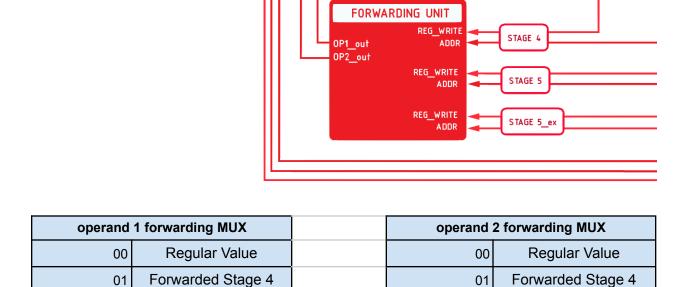

Data hazards mean the data dependencies between instructions. We have implemented two forwarding units inside stage three and stage 4. There are several methods to handle data hazards. The easy and basic method is to insert bubbles into the pipeline if there are data dependencies. This is an easy approach, but this method decreases the efficiency of the pipeline. The second method is to use forwarding methods. That means taking the ALU results from stages 4 and 5 as operand 1 and operand 2 in the execution stage. The following diagram shows the results that should be forwarded in order to handle the dependency data hazards.

Clock cycle

The following diagram shows how we handle the forwarding in various stages.

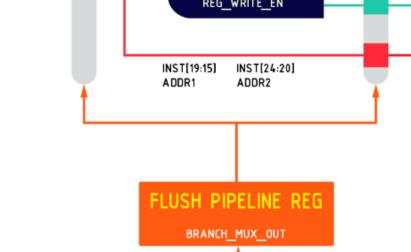

## This forwarding unit keeps the eye on operand 1 and operand 2 and checks whether there are new values for those lines in Stage 4 or Stage 5. If that is the case the forwarding unit sends the

ADDR2

10

11

0(\$2)

Forwarded Stage 5

Forwarded extra stage

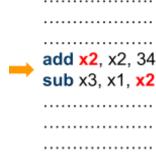

sequence that causes a hazard in this stage is the following.

Stage 3 (Execution Stage) forwarding unit

units.

signal to the Hazard Handling Muxes in operand 1 and operand 2 data paths. Data dependency could happen even between 3 stages apart. To be more clear, data that are in the write back stage are not written to the reg file while the instruction at the decode

stage fetches old data from the reg file. Therefore the forwarding unit should forward the data that is currently in the writeback stage at the next clock edge. Since there is no buffer to hold the data that will be omitted from the stage 5 (WB) pipeline register. To hold those data an additional pipeline register set was used. The inputs to and the outputs from the hazard handling units are as mentioned below. INST[19:15] INST[24:20]

10

11

Forwarded Stage 5

Forwarded extra stage

## 1w x3, 8(x0)sw x3, 8(x0)

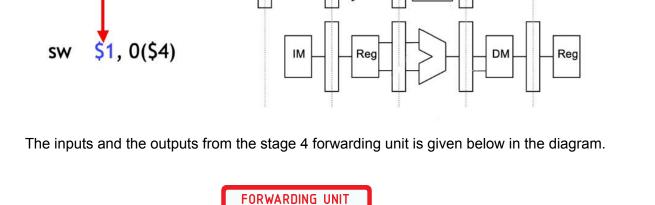

Stage 4 (Main Memory access Stage) forwarding unit

6

This forwarding unit keeps the eye on hazards happening in stage 4. The only instruction

stage 4 forwarding unit 0 Regular value stage 4 MEM READ

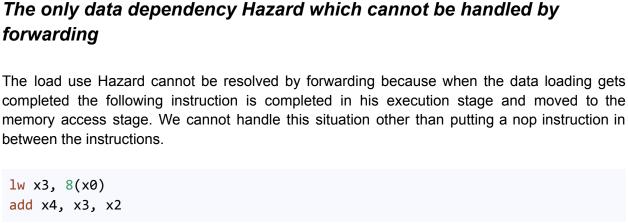

1w x3, 8(x0)add x4, x3, x2

• Control Hazard Handling

branch, then the first two pipeline registers get flushed so the two instructions loaded before the jump instructions are flushed.

Control hazards occur when the instruction flow is diverted because of branching. In order to handle this hazard we have to flush a few pipeline stages. We have connected the first two pipeline registers flushing lines. If the branch control unit decides the current instruction as a