RV32IM Pipeline Implementation

Table of Contents

Introduction

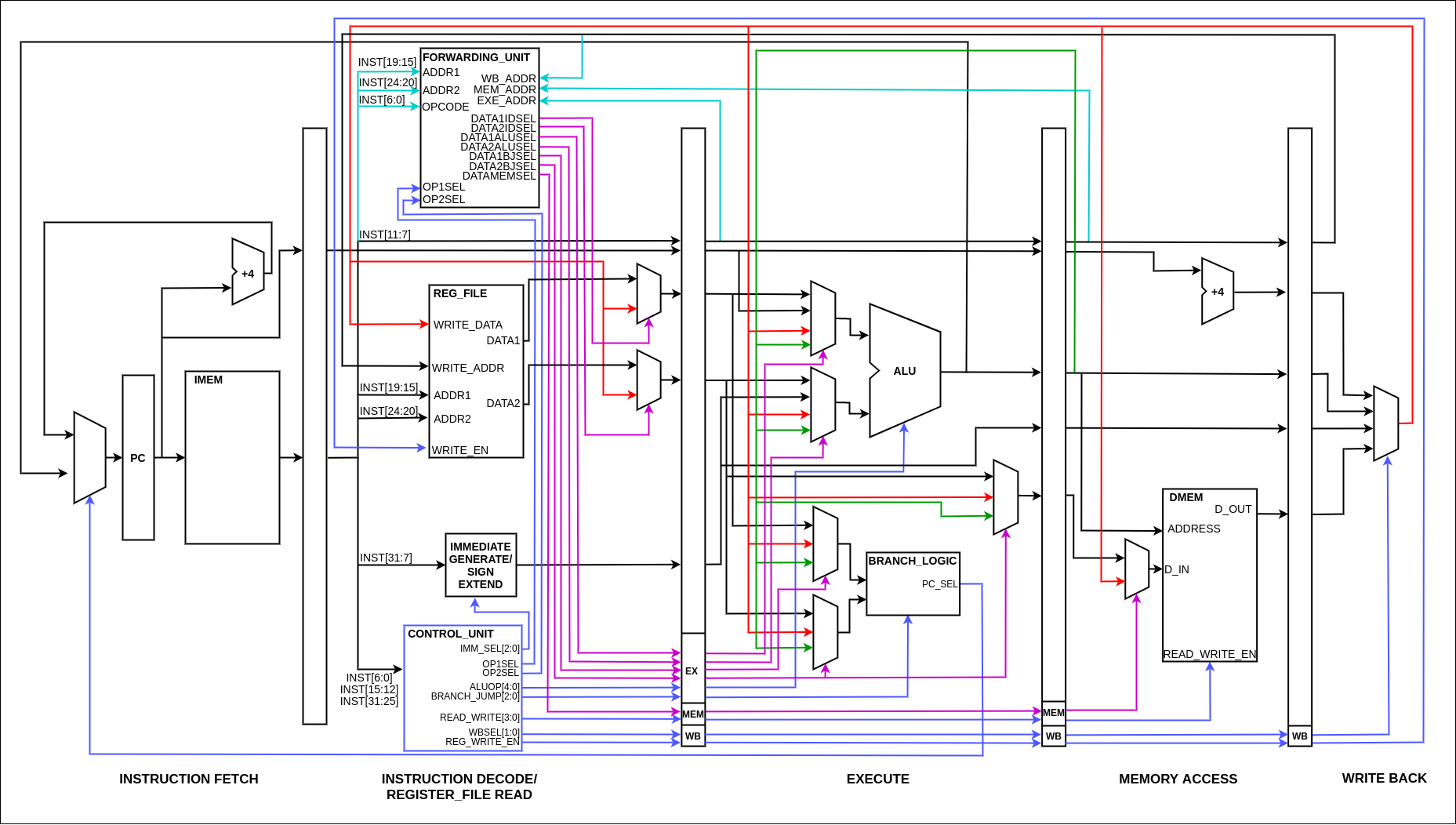

The objective of this project was to design and implement a 5 stage pipeline CPU to support the RISC-V instruction architecture. This pipeline CPU supports the entire RV32IM ISA which contains 45 instructions. The designed pipeline CPU was implemented using behavioral modeling in verilogHDL and icarus Verilog was used compile and simulate. gtkWave was used to observe the behavior.

Pipeline Datapath

Team

Supervisors

- Dr. Isuru Navinna

- Dr. Mahanama Wickramasinghe